# **Preliminary User's Manual**

# V850E/CA2<sup>TM</sup> JUPITER

32-/16-bit Romless Microcontroller

Hardware

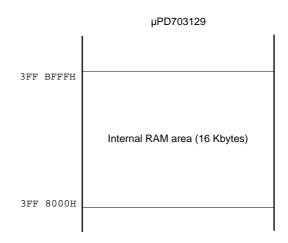

µPD703128, µPD703129

Document No. U15839EE1V0UM00 Date Published August 2003

© NEC Corporation 2003 Printed in Germany

#### NOTES FOR CMOS DEVICES

#### **1** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

## (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

- The information in this document is current as of 18.08, 2003. The information is subject to change

without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or

data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products

and/or types are available in every country. Please check with an NEC sales representative for

availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such NEC Electronics products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC Electronics no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics

products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated

entirely. To minimize risks of damage to property or injury (including death) to persons arising from

defects in NEC Electronics products, customers must incorporate sufficient safety measures in their

design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customerdesignated "quality assurance program" for a specific application. The recommended applications of NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact NEC Electronics sales representative in advance to determine NEC Electronics 's willingness to support a given application.

- **Notes: 1.** "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- **2.** "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

M8E 02.10

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- Ordering information

- Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### NEC Electronics Inc. (U.S.)

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### NEC Electronics (Europe) GmbH

Duesseldorf, Germany Tel: 0211-65 03 01 Fax: 0211-65 03 327

#### Sucursal en España

Madrid, Spain Tel: 091- 504 27 87 Fax: 091- 504 28 60

#### Succursale Française

Vélizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99 Filiale Italiana Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

#### Branch The Netherlands

Eindhoven, The Netherlands Tel: 040-244 58 45 Fax: 040-244 45 80

#### **Branch Sweden**

Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

#### United Kingdom Branch

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

## NEC Electronics Hong Kong Ltd.

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

## NEC Electronics Hong Kong Ltd.

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

#### NEC Electronics Singapore Pte. Ltd.

Singapore Tel: 65-6253-8311 Fax: 65-6250-3583

#### NEC Electronics Taiwan Ltd.

Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

#### NEC do Brasil S.A.

Electron Devices Division Guarulhos, Brasil Tel: 55-11-6465-6810 Fax: 55-11-6465-6829

## Preface

| Readers      | This manual is intended<br>V850E/CA2 (nickname 、 | for users who want to understand the functions of the Jupiter).                                                                                                      |

|--------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose      | This manual presents th                          | e hardware manual of V850E/CA2.                                                                                                                                      |

| Organization | This system specification                        | n describes the following sections:                                                                                                                                  |

|              | Pin function                                     |                                                                                                                                                                      |

|              | CPU function                                     |                                                                                                                                                                      |

|              | Internal peripheral fu                           | nction                                                                                                                                                               |

| Legend       | Symbols and notation a                           | e used as follows:                                                                                                                                                   |

|              | Weight in data notation                          | Left is high-order column, right is low order column                                                                                                                 |

|              | Active low notation                              | xxx (pin or signal name is over-scored) or<br>/xxx (slash before signal name)                                                                                        |

|              | Memory map address:                              | High order at high stage and low order at low stage                                                                                                                  |

|              | Note                                             | Explanation of (Note) in the text                                                                                                                                    |

|              | Caution                                          | tem deserving extra attention                                                                                                                                        |

|              | Remark                                           | Supplementary explanation to the text                                                                                                                                |

|              | Numeric notation                                 | Binary xxxx or xxxB<br>Decimal xxxx<br>Hexadecimal xxxxH or 0x xxxx                                                                                                  |

|              | Prefixes representing po                         | wers of 2 (address space, memory capacity)<br>K (kilo) : $2^{10} = 1024$<br>M (mega) : $2^{20} = 1024^2 = 1,048,576$<br>G (giga) : $2^{30} = 1024^3 = 1,073,741,824$ |

|        |            | Preface                                                               | 5          |

|--------|------------|-----------------------------------------------------------------------|------------|

| Chapt  | or 1       | I Introduction                                                        | 22         |

| -      | l.1        | General                                                               |            |

|        | 1.1        | Device Features                                                       |            |

|        | 1.2        | Application Fields                                                    |            |

|        | 1.3<br>1.4 | Ordering Information                                                  |            |

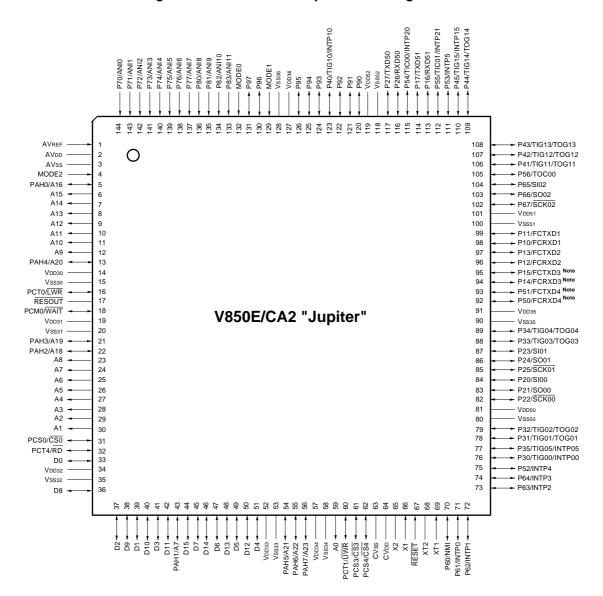

|        | 1.4        | Pin Configuration (Top View).                                         |            |

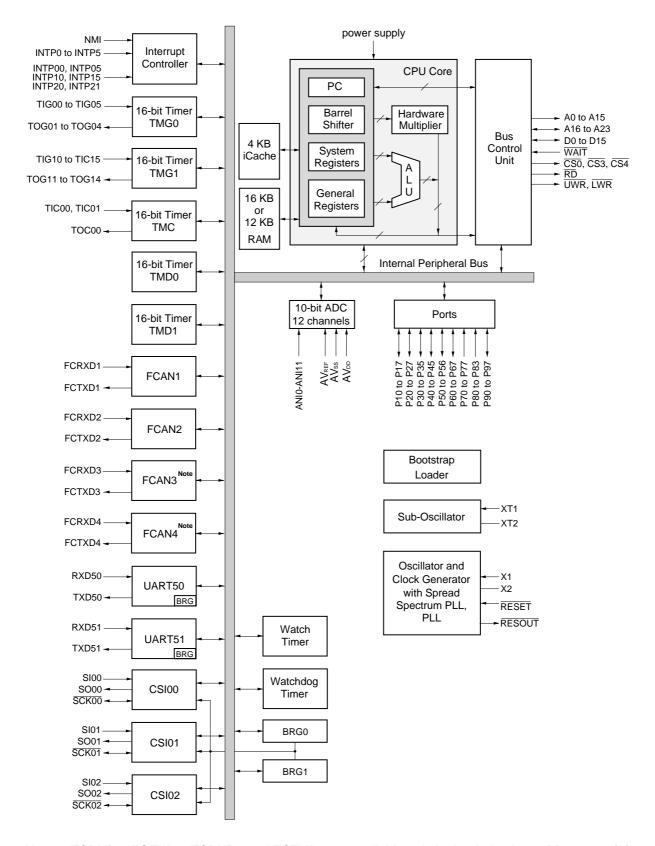

|        | 1.5        | Function Block Diagram.                                               |            |

|        | 1.0        | 1.6.1 On-chip units.                                                  |            |

|        |            |                                                                       |            |

| Chapt  |            |                                                                       |            |

|        | 2.1        | List of Pin Functions                                                 |            |

|        | 2.2        | Description of Pin Functions                                          |            |

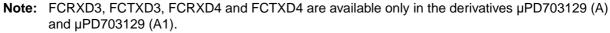

| 2      | 2.3        | Types of Pin I/O Circuit and Connection of Unused Pins                | 51         |

| Chant  |            | 3 CPU Function                                                        | <b>6 6</b> |

| Chapt  |            |                                                                       |            |

|        | 3.1<br>3.2 | Features                                                              |            |

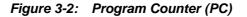

|        | _          | CPU Register Set                                                      |            |

|        |            | 3.2.1 Program register set                                            |            |

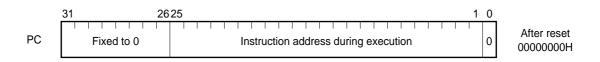

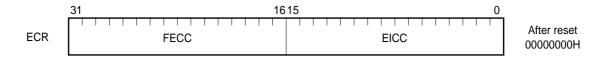

|        |            | 3.2.2 System register set                                             |            |

| :<br>: | 3.3        |                                                                       |            |

|        |            | <ul><li>3.3.1 Operation modes</li></ul>                               |            |

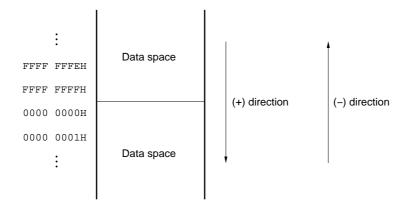

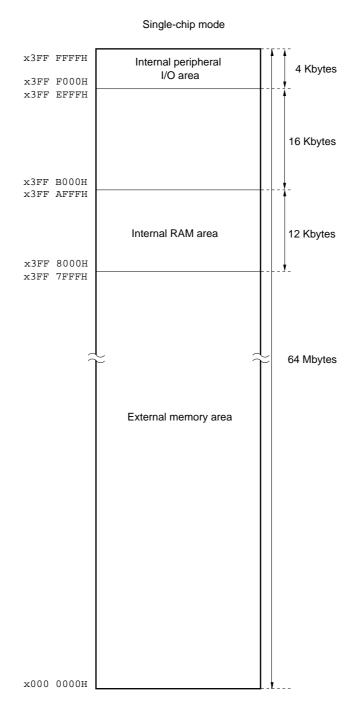

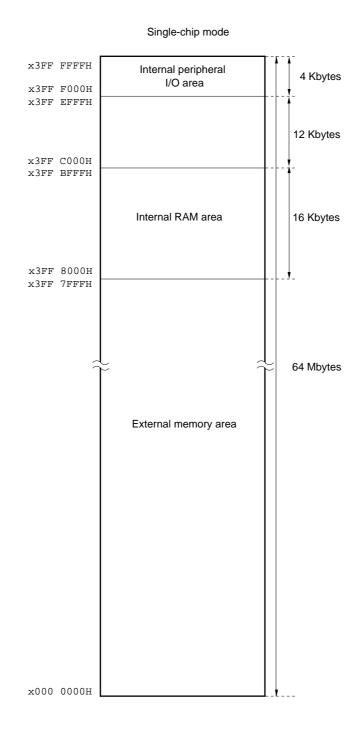

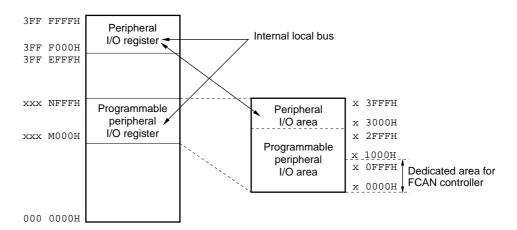

|        |            | Address Space                                                         |            |

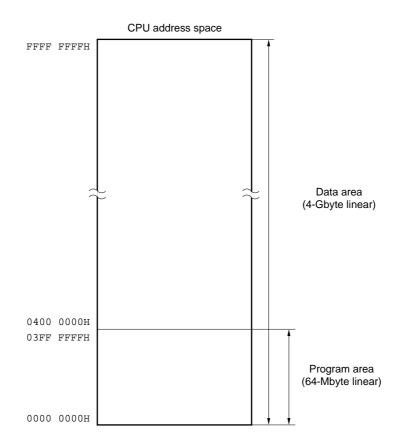

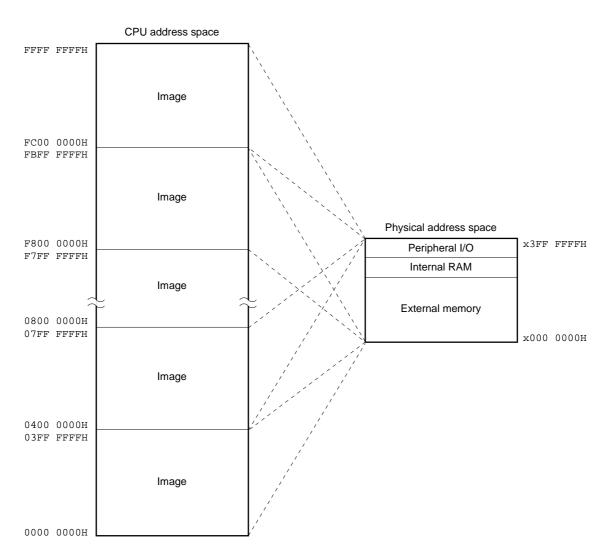

|        |            | 3.4.1 CPU address space                                               |            |

|        |            |                                                                       |            |

|        |            |                                                                       |            |

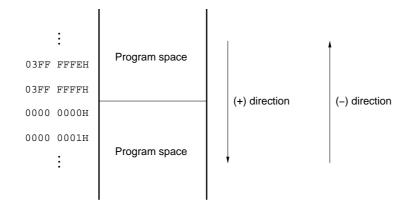

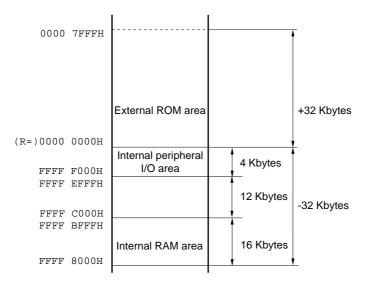

|        | 3.5        | 3.4.3 Wrap-around of CPU address space                                |            |

|        |            |                                                                       |            |

|        |            | 3.5.1       Area         3.5.2       Recommended use of address space |            |

|        |            | 3.5.3 Peripheral I/O Registers                                        |            |

|        |            | 3.5.4 Programmable peripheral I/O registers                           |            |

| -      | 3.6        |                                                                       |            |

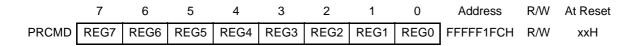

|        |            | 3.6.1 Command Register (PRCMD)                                        |            |

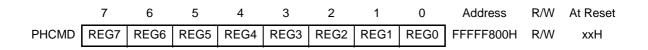

|        |            | 3.6.2 Peripheral Command Register (PHCMD)                             |            |

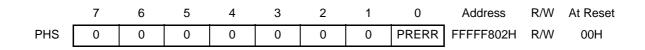

|        |            | 3.6.3 Peripheral Status Register (PHS)                                |            |

|        |            | 3.6.4 Internal peripheral function wait control register (VSWC)       | 107        |

|        |            |                                                                       | . 107      |

| Chapt  | er 4       | Bus Control Function                                                  | 109        |

| - 4    | 4.1        | Features                                                              | . 109      |

| 4      | 1.2        | Bus Control Pins                                                      | . 109      |

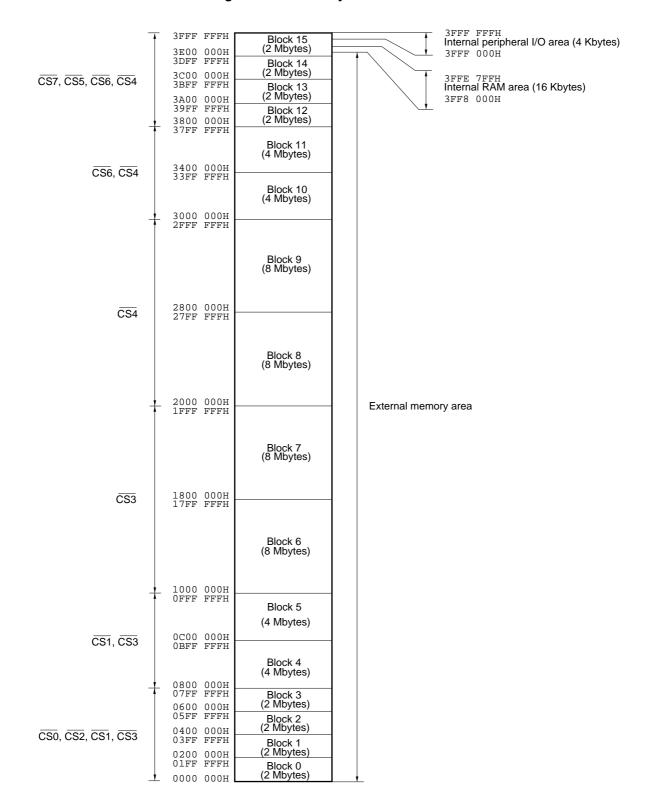

| 4      | 1.3        | Memory Block Function                                                 | . 110      |

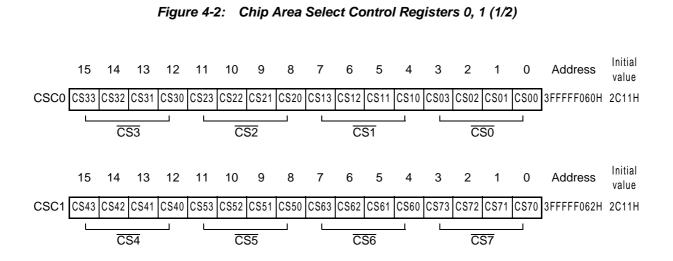

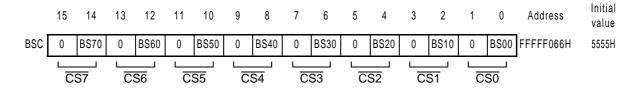

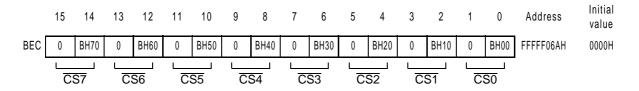

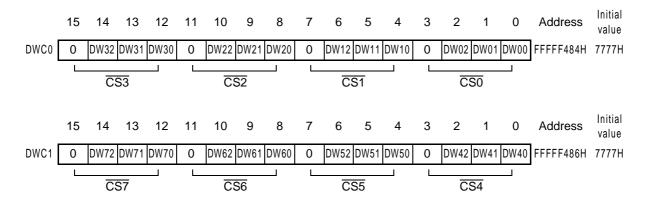

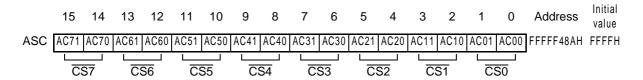

|        |            | 4.3.1 Chip Select Control Function                                    | . 111      |

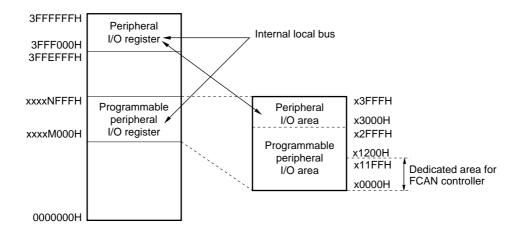

| 4      | 4.4        | Programmable peripheral I/O registers                                 | . 113      |

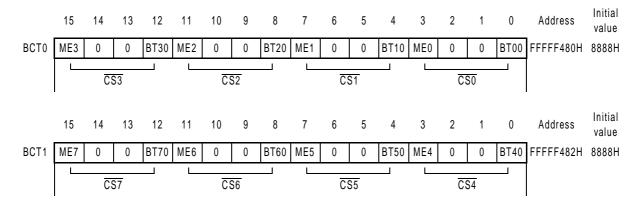

| 4      | 4.5        | Bus Cycle Type Control Function                                       | . 115      |

|        |            | 4.5.1 Bus cycle type configuration                                    |            |

| 4      | 4.6        | Bus Access                                                            |            |

|        |            | 4.6.1 Number of access clocks                                         |            |

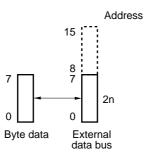

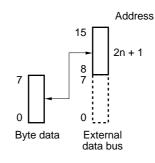

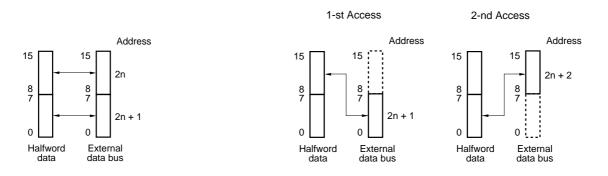

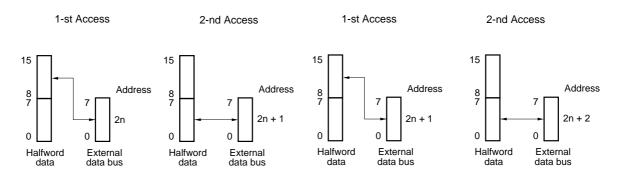

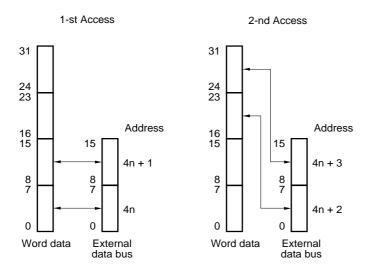

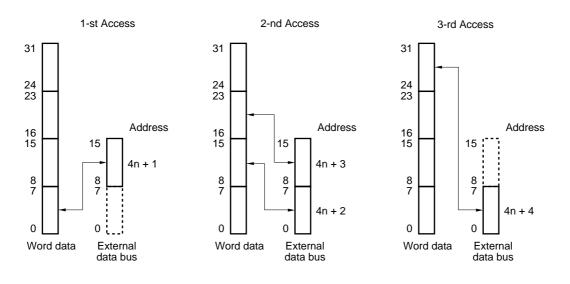

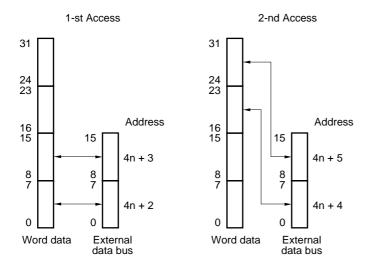

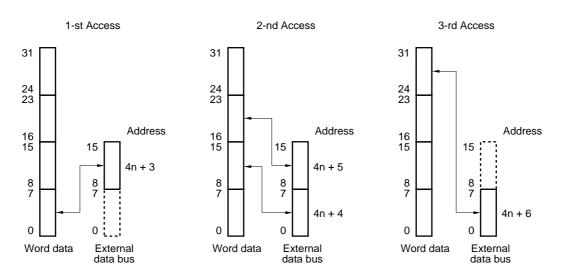

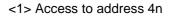

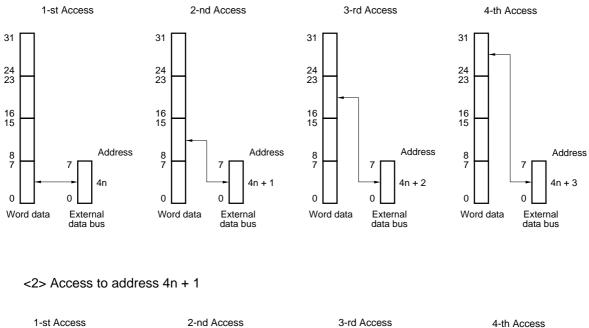

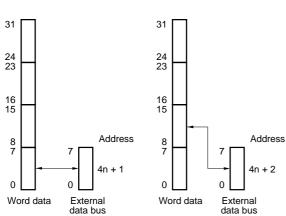

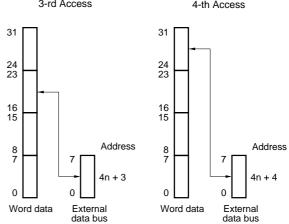

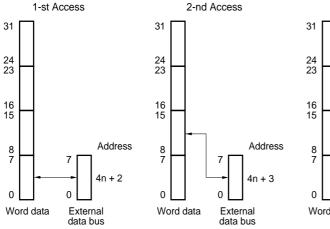

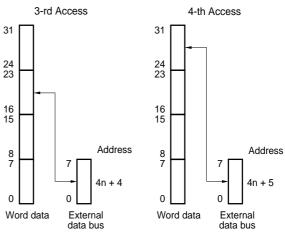

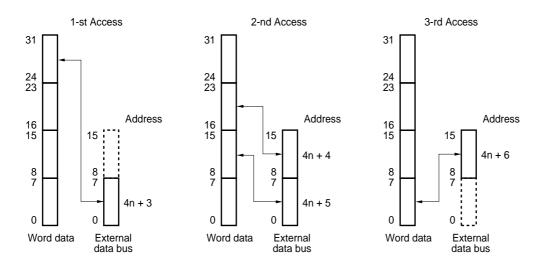

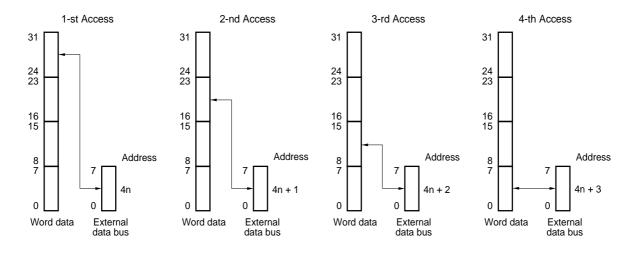

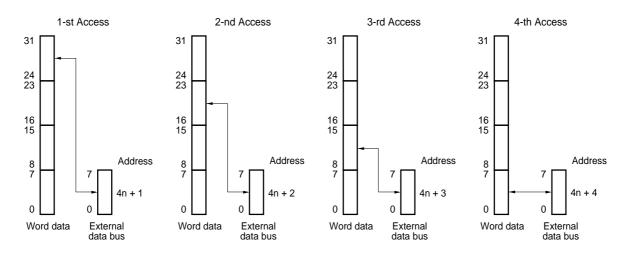

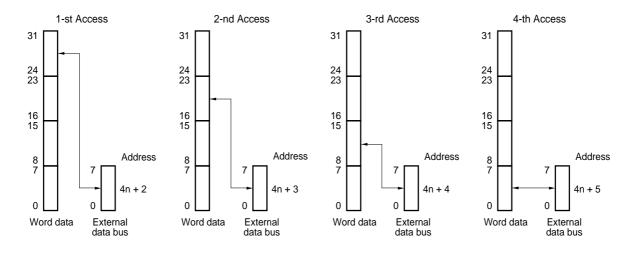

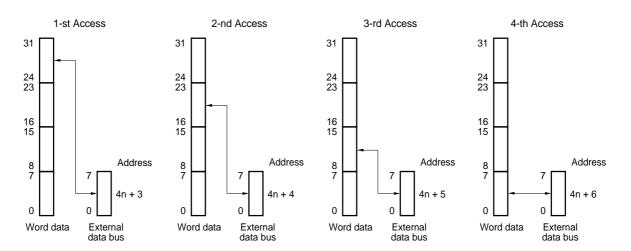

|        |            | 4.6.2 Bus sizing function                                             |            |

|        |            | 4.6.3 Endian control function                                         |            |

| 4      | 4.7        | Cache Configuration                                                   |            |

|        |            | 4.7.1 Bus width                                                       |            |

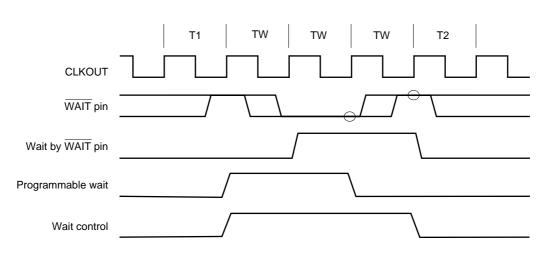

| 4      | 4.8        | Wait Function                                                         |            |

|        |            | 4.8.1 Programmable wait function                                      | . 131      |

## **Table of Contents**

|                                               | 4.8.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | External wait function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 133                                                                                                                                                                                                                   |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                               | 4.8.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Relationship between programmable wait and external wait                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 133                                                                                                                                                                                                                   |

| 4.9                                           | Idle S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | State Insertion Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 134                                                                                                                                                                                                                   |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Priority Order                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                       |

| 4.1                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | dary Operation Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                       |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Program space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                       |

|                                               | 4.11.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Data space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 136                                                                                                                                                                                                                   |

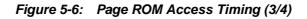

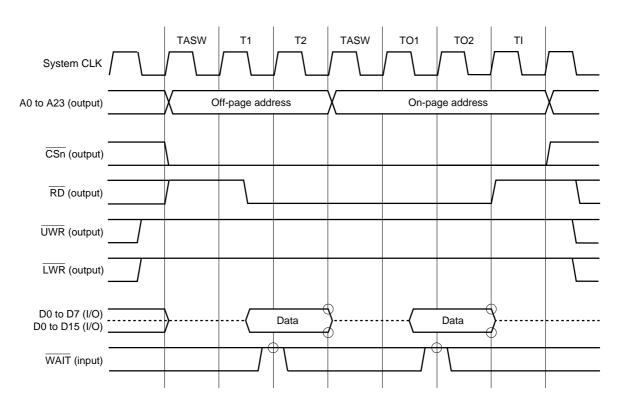

| Chanter                                       | 5 Ma                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | many Assess Control Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 407                                                                                                                                                                                                                   |

| Chapter<br>5.1                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | mory Access Control Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                       |

| <b>J</b> .I                                   | 5.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | M, External ROM, External I/O Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       |

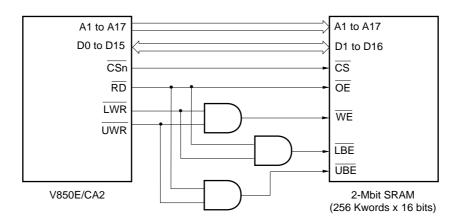

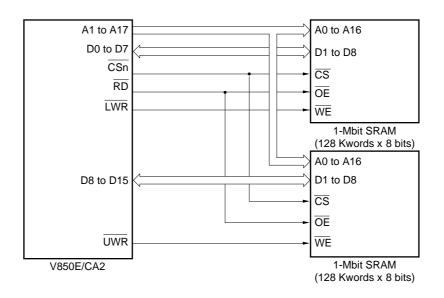

|                                               | 5.1.1<br>5.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SRAM connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                       |

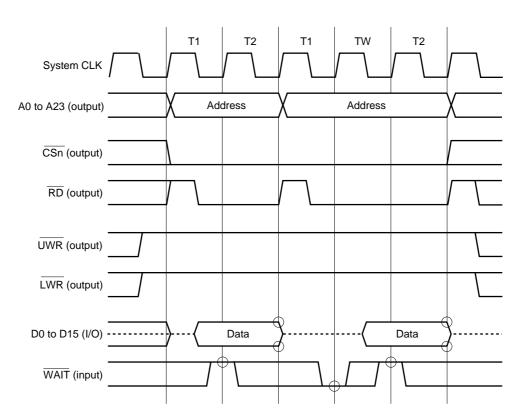

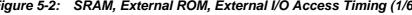

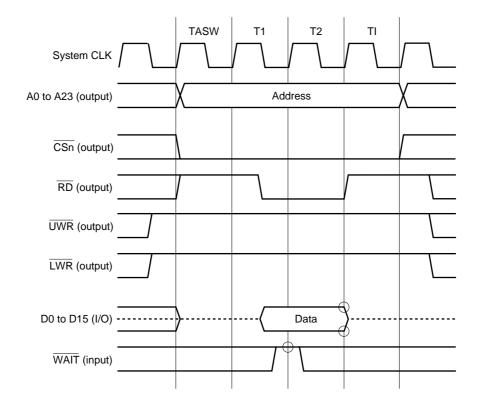

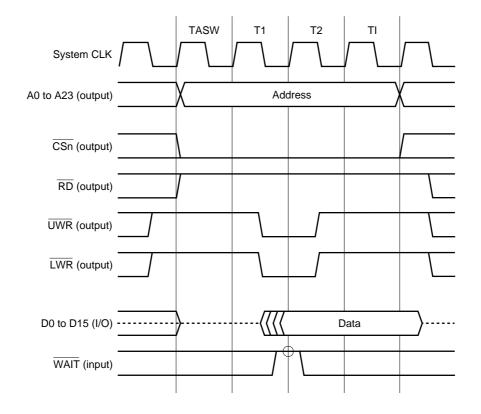

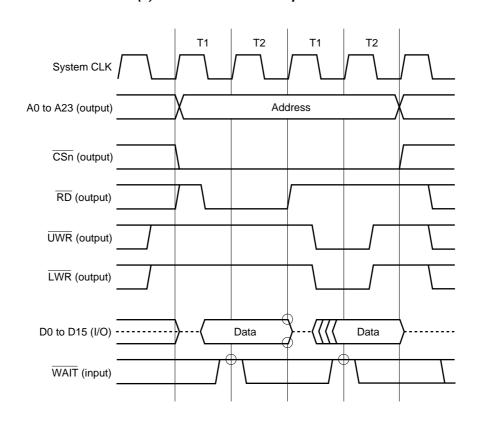

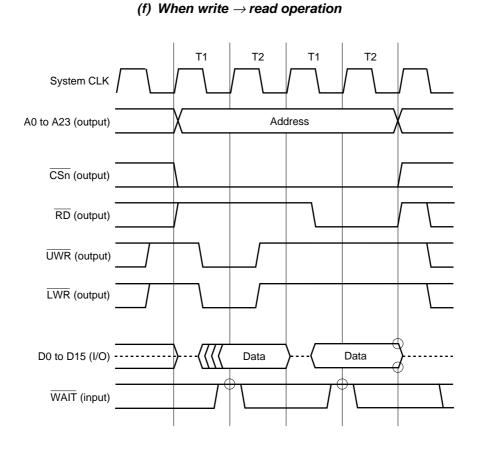

|                                               | 5.1.2<br>5.1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SRAM, external ROM, external I/O access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                       |

| 5.2                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ROM Controller (ROMC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       |

| J.Z                                           | 5.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                       |

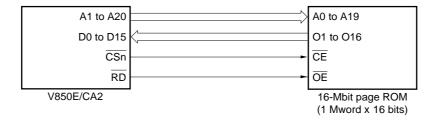

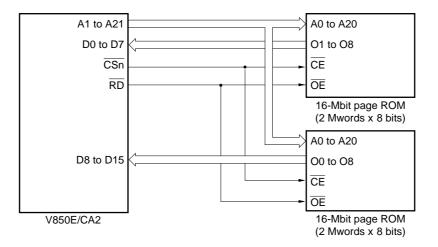

|                                               | 5.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page ROM connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                       |

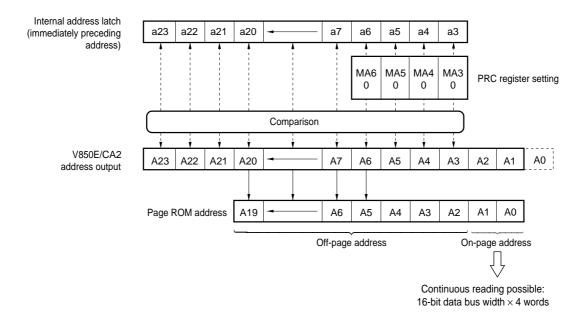

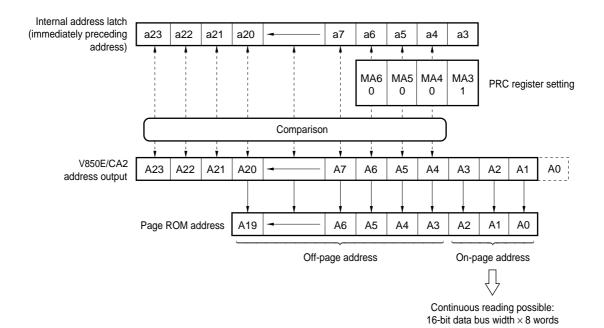

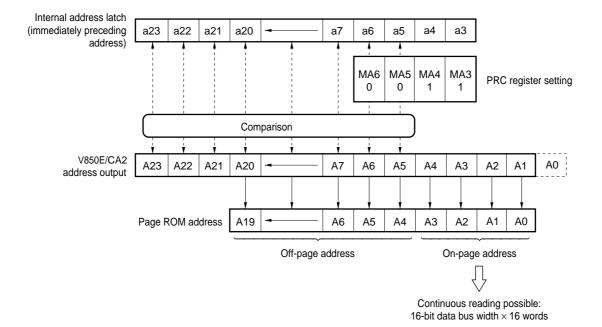

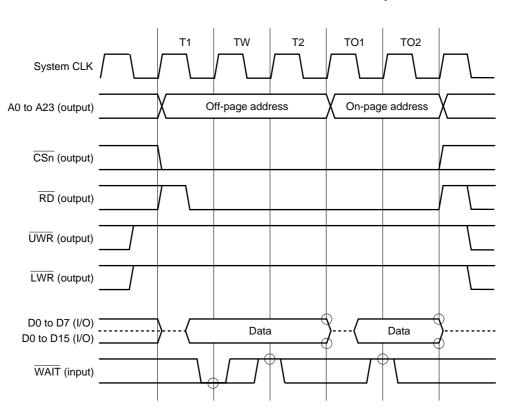

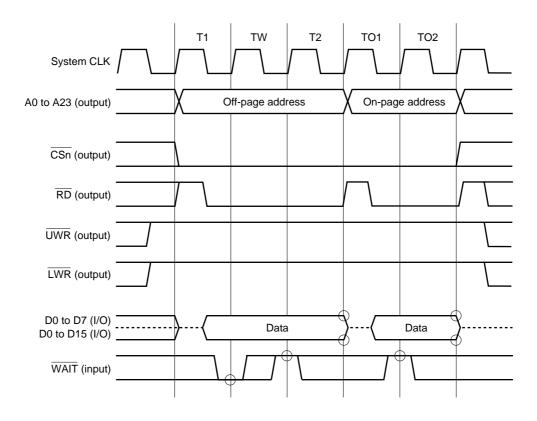

|                                               | 5.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | On-page/off-page judgment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                       |

|                                               | 5.2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page ROM configuration register (PRC).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |